# Pulse Control LSI for Serial Bus Control PCD2112A User's manual

# [Preface]

Thank you for choosing "PCD2112A" pulse controlled LSI.

Please read this manual thoroughly to become familiar with PCD2112A before using it.

Please note that the "Handling Precautions" concerning the mounting of this product are explained at the end of this manual.

# [Precautions for indications]

- 1) Reproduction of this manual, in whole or in part, is prohibited by the Copyright Act.

- 2) The contents of this manual are subject to change without prior notice in accordance with performance and quality improvement.

- 3) The contents of this manual are intended to be thorough, but should you find any uncertain subject, errors, or missing information, please feel free to contact us.

- 4) Regardless of the abovementioned items, we are not liable for any damages caused by the use of this product.

# [Description]

- Negative logic terminal names and negative logic signal names are not decorated with overbar nor "#".

For the logics, see "3.3 Terminal functions".

- 2) "0" in bit description of registers etc. indicates the bit position and that only "0" can be written and only "0" can be read out.

- 3) The specific bit of a register is shown as "register name. bit name"; (e.g. RMD.MSDE)

- 4) In the description of operating speed, when the subject is applied for both "FH1" and "FH2", they are collectively referred to as "FH". In the explanation of registers for speed, "RFH1" and "RFH2" speed registers are also collectively referred to as "RFH". In the explanation of commands, "STAFH1" and "STAFH2" are also collectively referred to as "STAFH".

- 5) In the description of end limit terminals, when the subjects are common to both "PEL terminal" and "MEL terminal", they are collectively referred to as "EL terminals".

- In the description of end limit signals, when they are common both to "PEL signal" and "MEL signal", they are also collectively referred to as "EL signals".

- 6) If the time is indicated, the value of "Reference clock frequency = 9.8304 MHz" is indicated unless otherwise specified.

- 7) There are "ON" and "OFF" in the signal status. In the case of positive logic, "H level" or "1" is "ON" state. In the case of negative logic, "L level" or "0" is "ON" state.

- 8) The value suffix "b" represents a binary number, and "h" represents a hexadecimal number. Suffixes are not added to decimal numbers.

- Suffixes may not be added to binary and hexadecimal numbers for some figures, tables, or values that are the same as decimal numbers.

# **INDEX**

| 1. Outline and features                                      | 1  |

|--------------------------------------------------------------|----|

| 1.1 Outline                                                  | 1  |

| 1.2 Features                                                 | 1  |

| 2. Specifications                                            | 2  |

| 2.1 Basic specifications                                     | 2  |

| 2.2 Terminal assignment diagram                              | 3  |

| 2.3 Block diagram                                            | 3  |

| 2.4 Terminal list                                            | 4  |

| 2.5 System modes                                             | 5  |

| 2.5.1 CPU-connected system (MODE = L)                        |    |

| 2.5.2 Stand-alone operation system (MODE = H)                | 7  |

| 3. Terminal descriptions                                     | 8  |

| 3.1 Outline of terminal functions                            | 8  |

| 3.2 Terminal functions in each system mode                   | 9  |

| 3.3 Terminal functions                                       | 10 |

| 3.3.1 CLK [7]                                                | 10 |

| 3.3.2 RST [3]                                                | 10 |

| 3.3.3 MODE [5]                                               | 10 |

| 3.3.4 MTYP [33]                                              | 10 |

| 3.3.5 INT [4]                                                | 11 |

| 3.3.6 SCK [40], DI [35], DO [36], CS [38], CSO [34]          | 11 |

| 3.3.7 PA/PDR [9], PB/MDR [10]                                | 11 |

| 3.3.8 A0/PS0 [44], A1/PS1 [45], PS2 [46], PS3 [47], PS4 [48] | 12 |

| 3.3.9 EA [11], EB [12], EZ [13]                              | 12 |

| 3.3.10 BSY/END [20]                                          | 12 |

| 3.3.11 SD [15]                                               | 12 |

| 3.3.12 PELL [22], MELL [21]                                  | 13 |

| 3.3.13 PEL [17], MEL [16]                                    | 13 |

| 3.3.14 ORG [14]                                              |    |

| 3.3.15 STA [42]                                              | 13 |

| 3.3.16 STP [43]                                              | 13 |

| 3.3.17 OUT/PH1 [26], DIR/PH2 [27]                            | 14 |

| 3.3.18 ERC/CDW [19]                                          | 14 |

| 3.3.19 UB [24]                                               | 14 |

| 3.3.20 INP/FH [23]                                           | 14 |

| 3.3.21 P0 [1], P1 [2]                                        | 15 |

| 3.3.22 P2/PH3 [28], P3/PH4 [29]                              | 15 |

| 3.3.23 VDD [8, 30, 41], GND [6, 18, 25, 31, 32, 37, 39]      | 15 |

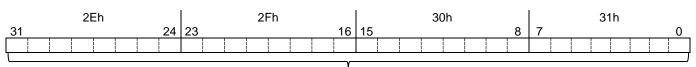

| 4. Memory map                                                | 16 |

| 4.1 Detailed memory map                                      | 17 |

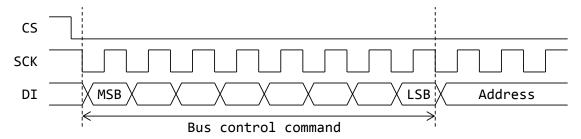

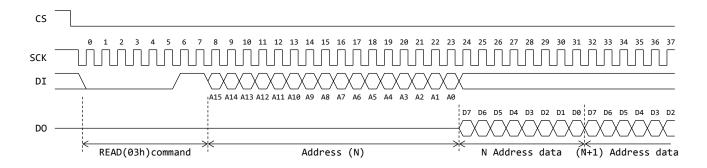

| 5. Serial communication format                               | 18 |

| 5.1 Bus control command                                      | 18 |

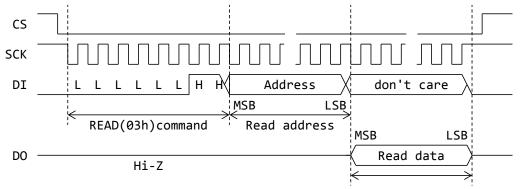

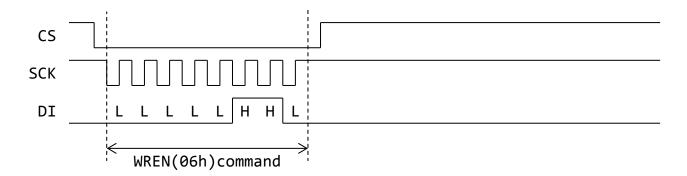

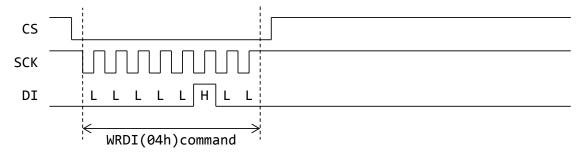

| 5.2 Basic operations                                         | 19 |

| 5.3 Read operation from PCD2112A                             | 19 |

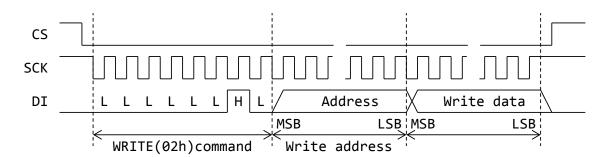

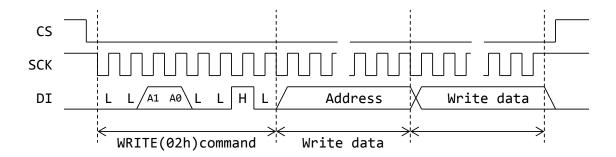

| 5.4 Write operation to "PCD2112A"                             | 19 |

|---------------------------------------------------------------|----|

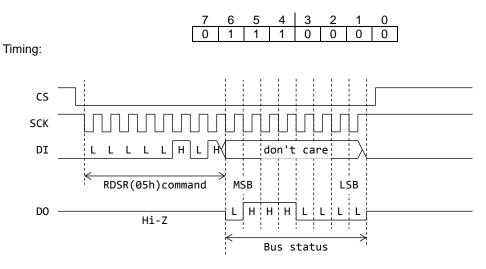

| 5.5 Reading bus status operation                              | 20 |

| 5.6 Transition to EEPROM access mode                          | 20 |

| 5.7 Terminating EEPROM access mode                            | 21 |

| 5.8 EEPROM control                                            | 21 |

| 5.9 Multiple LSI connections                                  | 22 |

| 6. Commands                                                   | 23 |

| 6.1 Operation command                                         | 24 |

| 6.1.1 Start command                                           | 24 |

| 6.1.2 Remaining-pulse start command                           | 24 |

| 6.1.3 Speed-change command                                    | 24 |

| 6.1.4 Stop command                                            | 24 |

| 6.2 Control command                                           | 25 |

| 6.2.1 Software reset command                                  | 25 |

| 6.2.2 Counter zero-clear command                              | 25 |

| 6.2.3 ERC signal output control command                       | 25 |

| 6.2.4 STA signal output control command                       | 25 |

| 6.2.5 Other commands                                          | 25 |

| 7. Registers                                                  | 26 |

| 7.1 RMD: Operation mode setting register                      | 26 |

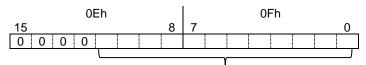

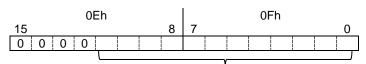

| 7.2 RMV: Number of output pulse setting register              | 27 |

| 7.3 RMG: Speed magnification setting register                 | 27 |

| 7.4 RFL: FL speed setting register                            | 27 |

| 7.5 RFH: FH speed setting register                            | 27 |

| 7.5.1 RFH1: FH1 speed setting register                        | 27 |

| 7.5.2 RFH2: FH2 speed setting register                        | 28 |

| 7.6 RUR: Acceleration rate setting register                   | 28 |

| 7.7 RDR: Deceleration rate setting register                   | 28 |

| 7.8 RUS: Acceleration S-curve section setting register        | 28 |

| 7.9 RDS: Deceleration S-curve section setting register        | 28 |

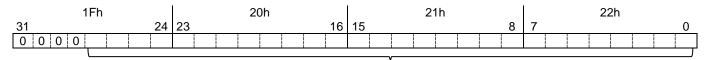

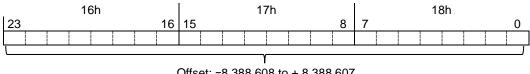

| 7.10 RDP: Slow-down point setting register                    | 29 |

| 7.11 RENV1: Environment setting 1 register                    | 29 |

| 7.12 RENV2: Environment setting 2 register                    | 32 |

| 7.13 RSTS: Status information register                        | 34 |

| 7.14 RIST: Interrupt factor reset register                    | 36 |

| 7.15 RSPD: Current speed reading register                     | 37 |

| 7.16 RCUN: Current position register                          | 37 |

| 7.17 RDWC: Remaining-pulse number reading register            | 37 |

| 7.18 RIOP: General-purpose I/O port configuration register    | 38 |

| 8. Operation mode                                             | 39 |

| 8.1 Command control: Continuous movement                      | 39 |

| 8.2 Origin signal control: Origin return                      | 39 |

| 8.3 Origin return with feeding amount limit                   | 39 |

| 8.4 Origin signal control: Origin escape operation            | 40 |

| 8.5 EL signal (End Limit signal) control: EL escape operation | 40 |

| 8.6 Positioning control: Incremental movement                 | 40 |

| 8.7 Positioning control: Timer                                             | 40 |

|----------------------------------------------------------------------------|----|

| 8.8 Switch control: Continuous movement                                    | 41 |

| 8.9 Switch control: Incremental movement                                   | 41 |

| 8.10 Pulser control: Continuous movement                                   | 42 |

| 8.11 Pulser control: Incremental movement                                  | 43 |

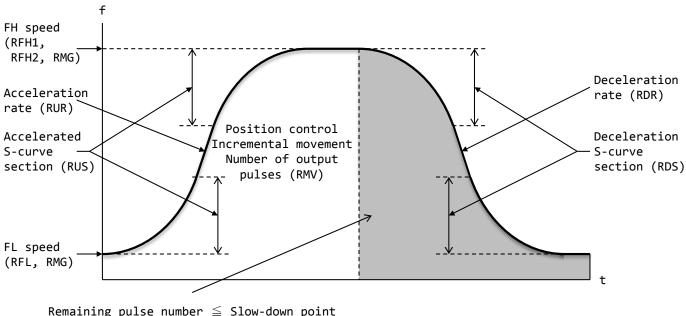

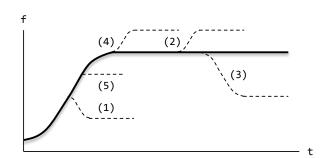

| 9. Speed pattern                                                           | 44 |

| 9.1 Speed pattern list                                                     | 44 |

| 9.2 Speed pattern setting                                                  | 45 |

| 9.2.1 RMV: Number of output pulses setting register (28 bits)              | 46 |

| 9.2.2 RFL: FL speed setting register (13 bits)                             | 46 |

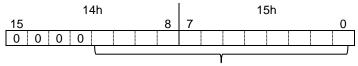

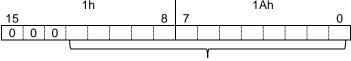

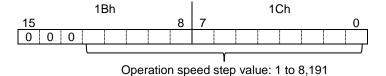

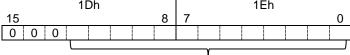

| 9.2.3 RFH: FH speed setting register (13 bits)                             | 46 |

| 9.2.4 RUR: Acceleration rate setting register (16 bits)                    | 47 |

| 9.2.5 RDR: Deceleration rate setting register (16 bits)                    | 47 |

| 9.2.6 RMG: Speed magnification setting register (12 bits)                  | 48 |

| 9.2.7 RDP: Slow-down point setting register (24 bits)                      | 49 |

| 9.2.8 RUS: Acceleration S-curve section setting register (12 bits)         | 50 |

| 9.2.9 RDS: Deceleration S-curve section setting register (12 bits)         | 50 |

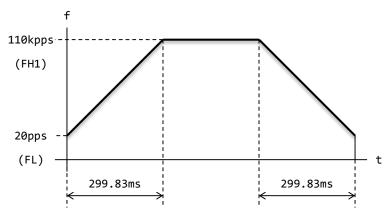

| 9.3 Manual FH correction calculation                                       | 51 |

| 9.3.1 Linear acceleration/deceleration                                     | 51 |

| 9.3.2 S-curve acceleration/deceleration without linear accel/decel section | 51 |

| 9.3.3 S-curve acceleration/deceleration with linear accel/decal section    | 52 |

| 9.4 Examples of speed pattern setting                                      | 54 |

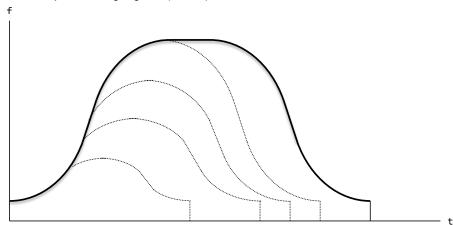

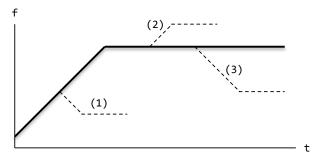

| 9.5 Target speed override                                                  | 55 |

| 10. Function description                                                   | 56 |

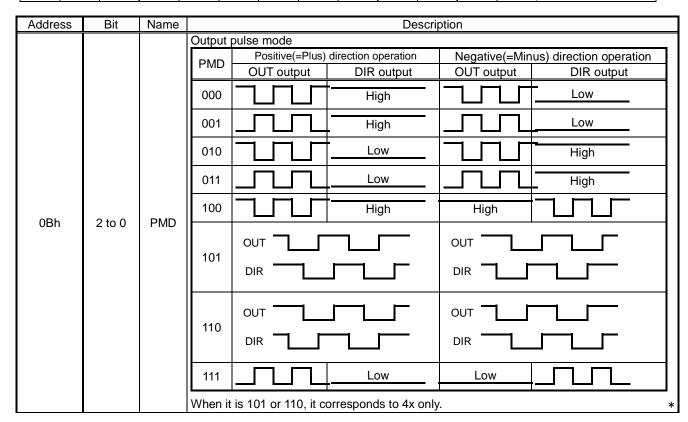

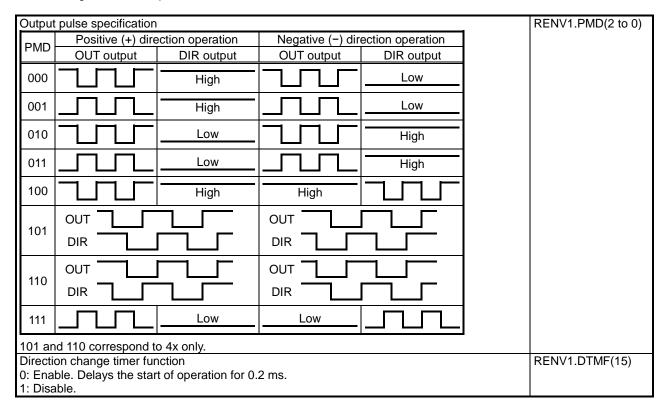

| 10.1 Output pulse control                                                  | 56 |

| 10.1.1 Output pulse mode and direction change timer                        | 56 |

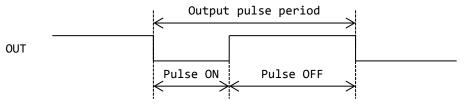

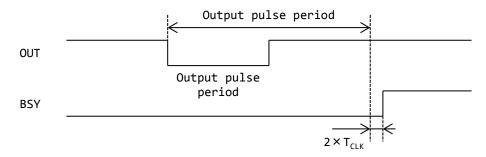

| 10.1.2 Output pulse width and operation complete timing                    |    |

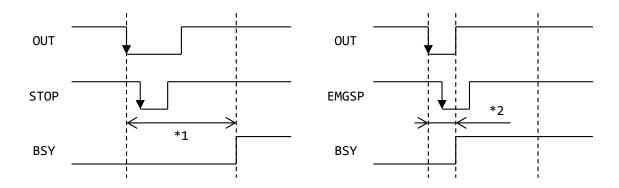

| 10.2 Operation state check output                                          | 57 |

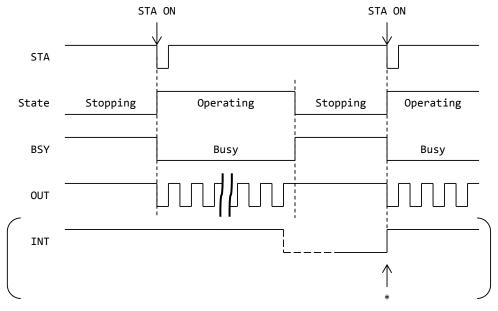

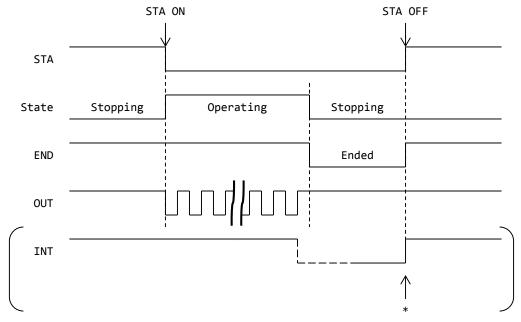

| 10.2.1 BSY signal                                                          | 57 |

| 10.2.2 END signal                                                          | 58 |

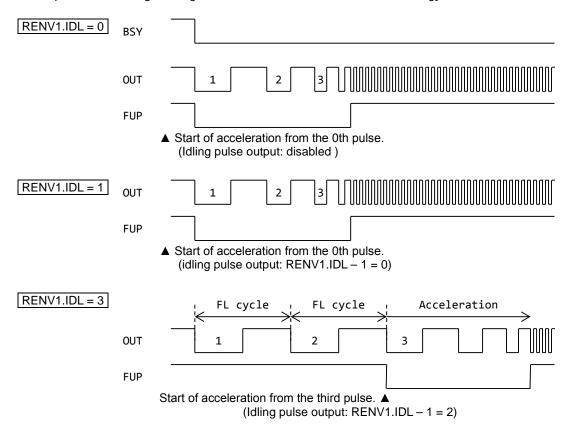

| 10.3 Idling control                                                        | 59 |

| 10.4 External mechanical signal input                                      | 60 |

| 10.4.1 PEL and MEL signals                                                 | 60 |

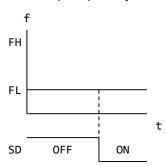

| 10.4.2 SD signal                                                           | 61 |

| 10.4.3 ORG signal and EZ signal                                            | 64 |

| 10.4.4 EA and EB signals                                                   | 65 |

| 10.5 Servo motor I/F                                                       | 66 |

| 10.5.1 INP signal                                                          | 66 |

| 10.5.2 ERC signal                                                          | 67 |

| 10.6 Stepping motor I/F                                                    | 68 |

| 10.6.1 CDW signal                                                          |    |

| 10.6.2 PH1 to PH4 signals                                                  | 69 |

| 10.7 External start and simultaneous start                                 | 70 |

| 10.7.1 STA signal in CPU-connected system                                  | 70 |

| 10.7.2 STA and PS0-PS4 signals in stand-alone operations                   |    |

| 10.8 External stop                                                         | 73 |

| 10.8.1 STP signal                                                          | 73 |

| 10.9 Counter                                                               | 74 |

| 10.9.1 Counter types and input methods                                        | 74 |

|-------------------------------------------------------------------------------|----|

| 10.9.2 Clearing the counter to zero                                           | 74 |

| 10.10 ID monitor                                                              | 75 |

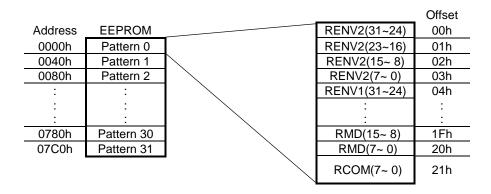

| 11. Supplementary description of stand-alone operation system                 | 76 |

| 11.1 EEPROM selection criteria                                                | 76 |

| 11.2 Set the data to EEPROM                                                   | 77 |

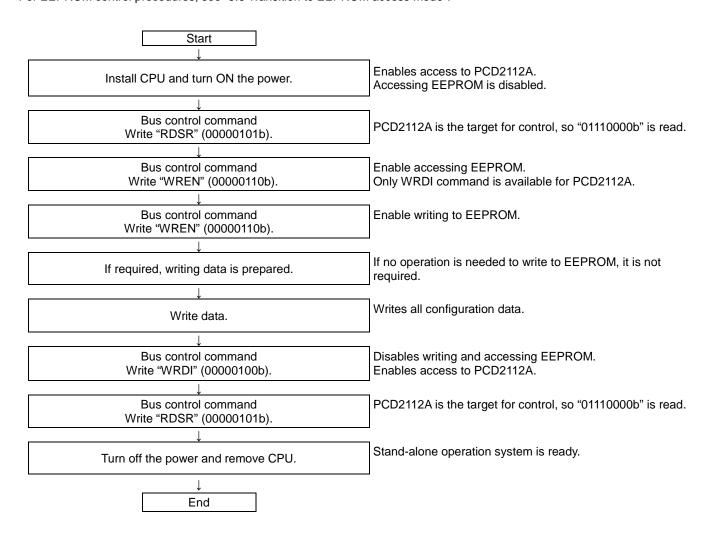

| 11.2.1 Set-up procedure                                                       | 77 |

| 11.2.2 EEPROM address map                                                     | 78 |

| 12. Electrical characteristics                                                | 79 |

| 12.1 Absolute maximum ratings                                                 | 79 |

| 12.2 Recommended operating conditions                                         | 79 |

| 12.3 DC characteristics                                                       | 79 |

| 12.4 AC characteristic                                                        | 80 |

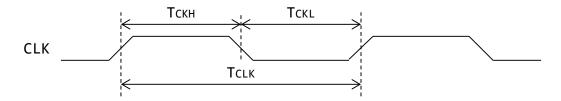

| 12.4.1 Reference clock                                                        | 80 |

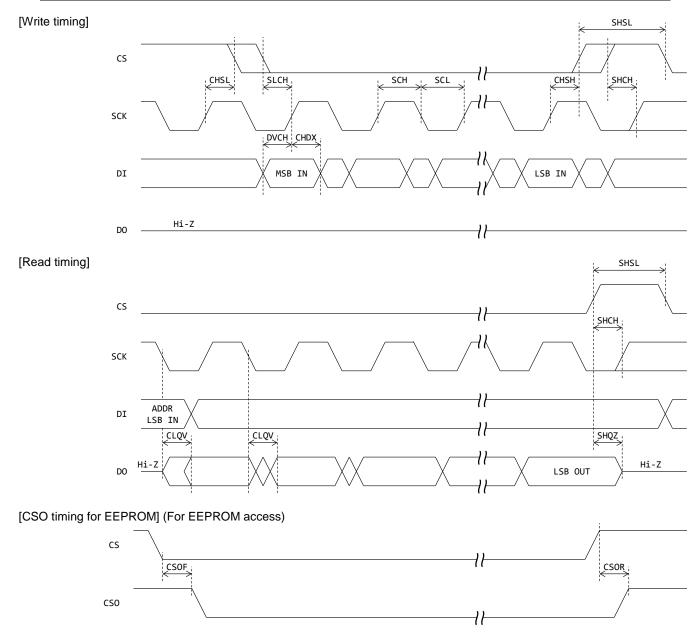

| 12.4.2 Serial bus I/F                                                         | 81 |

| 12.5 Operation timings                                                        | 82 |

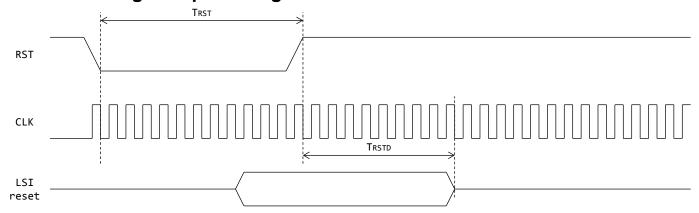

| 12.5.1 Reset signal input timing                                              | 83 |

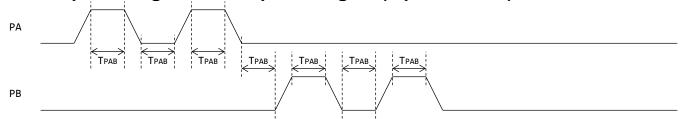

| 12.5.2 Input timing of manual pulser signal (2-pulse mode)                    | 83 |

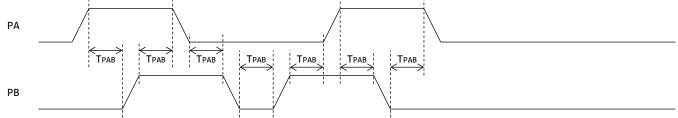

| 12.5.3 Input timing of manual pulser signal (90-degree phase difference mode) | 83 |

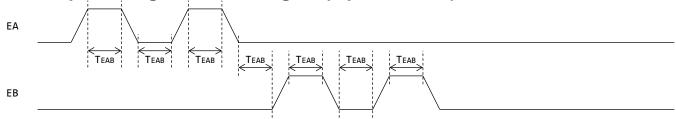

| 12.5.4 Input timing of encoder signal (2-pulse mode)                          | 83 |

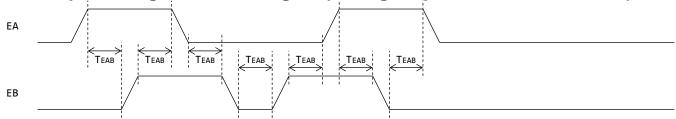

| 12.5.5 Input timing of encoder signal (90-degree phase difference mode)       | 83 |

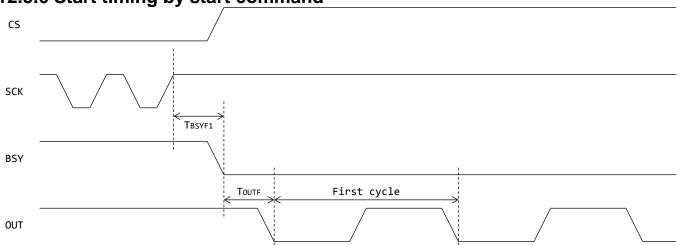

| 12.5.6 Start timing by start command                                          | 84 |

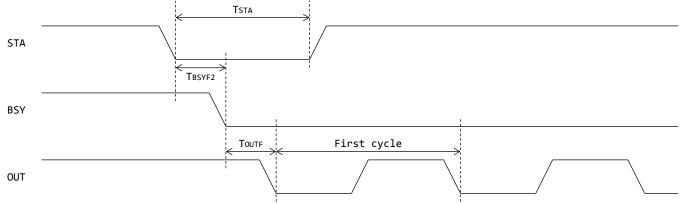

| 12.5.7 Start timing by start signal input                                     | 84 |

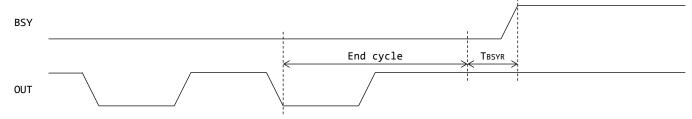

| 12.5.8 Operation complete timing                                              | 84 |

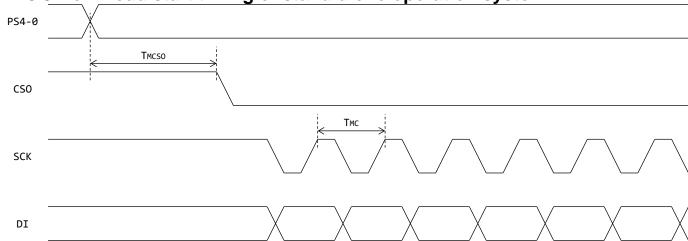

| 12.5.9 Download start timing of stand-alone operation system                  | 85 |

| 12.5.10 Download time of stand-alone operation system                         | 85 |

| 13. External dimensions                                                       |    |

| 14. Handling precautions                                                      | 87 |

| 14.1 Design Precautions                                                       | 87 |

| 14.2 Precautions for Transportation and Storage                               | 87 |

| 14.3 Precautions for Handling Environment                                     | 88 |

| 14.4 Precautions for mounting                                                 | 89 |

| 15. Differences between PCD2112A and PCD2112                                  | 90 |

| 15.1 Additional functions                                                     | 90 |

| 15.1.1 ID monitor                                                             | 90 |

| 15.2 Functional improvement                                                   | 90 |

| 15.2.1 SCK signal input before control target LSI change                      | 90 |

| 15.3 Correct non-conformity                                                   | 90 |

| 15.3.1 Writing emergency stop command during stopping                         | 90 |

| 15.3.2 Slow-down point auto-setting by target speed override                  | 90 |

| 15.4 Package changes                                                          |    |

| 15.4.1 Comparison of electrical characteristics                               |    |

| 15.4.2 Comparison of external dimensions                                      | 92 |

| 15.4.3 Comparison of precautions for mounting                                 | 03 |

### 1. Outline and features

### 1.1 Outline

PCD2112A is a pulse generator LSI that can connect to CPU by 4-wire serial bus I/F.

Serial bus I/F do not require many signal lines, unlike the parallel bus I/F.

A smaller package CPU can be selected, and general-purpose ports of CPU can be used effectively.

In addition to "CPU-connected system" controlled by CPU, "stand-alone operation system" operating with external EEPROM, is built-in.

### 1.2 Features

### Serial bus I/F

Since 4-wire serial bus is used to connect with CPU, the number of occupied terminals for bus control in CPU can be reduced, so that the number of open general-purpose I/O terminals increase.

From CPU, you can access to PCD2112A in the same way as 4-wire serial EEPROM.

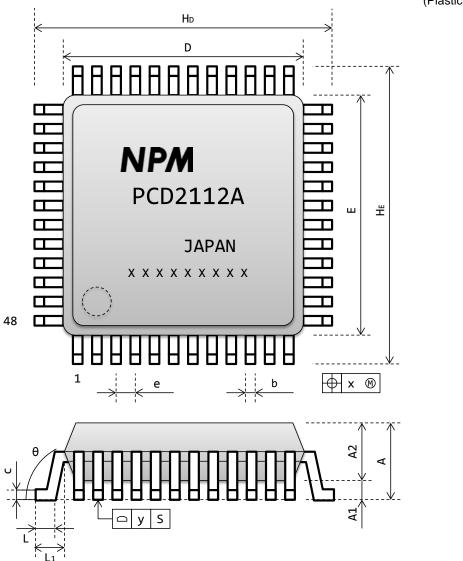

### ♦ Small package

The use of a serial bus has resulted in a compact package (TQFP-48) with multiple functions.

The external dimensions are 9 mm square, and the molded part is 7 mm square.

### 3.3 V single power supply

It operates with a single power supply of 3.3 V  $\pm$  0.3 V.

The output signal level is 3.3 V, but the input signal level can be 5 V (TTL).

### High-speed pulse train output

When the reference clock frequency is 9.8304 MHz (standard), 2.4 Mpps can be output.

When it is 20 MHz, with is the maximum frequency, up to 5 Mpps can be output.

Output pulse mode can be selected out of common-pulse (OUT and DIR), 2-pulses (positive and negative), and 90-degree phase difference 4x (= multiplication) (A-phase and B-phase).

### ◆ Excitation sequence signal output for 2-phase stepping motor

Two types of drive and two types of excitation can be used to output excitation sequence signals.

### ◆ Acceleration/deceleration control

Linear acceleration/deceleration and S-curve acceleration/deceleration can be performed.

For S-curve acceleration/deceleration, linear acceleration/deceleration sections can be inserted in the middle part (S-curve section setting). The acceleration and deceleration characteristics can be set independently (independent setting is not available when using slow-down point auto-setting function).

### Target speed override

Speed can be changed during operation.

### ◆ Triangle drive avoidance function (FH correction function)

When the total amount of feeding pulses is small, the maximum speed is automatically lowered to avoid triangular driving. This function is available for operation mode of incremental movement in positioning control and switch control.

### Simultaneous start function

When multiple LSIs are used and if all STA terminals are connected, they can start at the same time.

### ◆Various operation modes

- · Continuous movement (command control, manual pulser control, switch control)

- · Origin return (stop at origin sensor, feeding amount limit stop)

- · Escaping (Origin sensor, End limit sensor)

- · Incremental movement (positioning control, manual pulser control, switch control).

- Timer

### Stand-alone operation system

If you connect a 4-wire serial EEPROM to PCD2112A, controls can be done without connecting to CPU. Up to 32 types of operation patterns can be stored in EEPROM.

# 2. Specifications

# 2.1 Basic specifications

| Item                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Power supply                                        | +3.3 V ± 0.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Reference clock                                     | Standard: 9.8304 MHz (20 MHz max.)                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| CPU I/F                                             | 4-wire serial bus                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Output pulse number (=feeding amount) setting range | 0 to 268,435,455 (28 bit)                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Number of speed setting steps                       | 1 to 8,191 (13 bit)                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Speed magnification setting range                   | 0.5 to 300x (reference clock 9.8304 MHz)  0.5 x: 0.5 to 4,095.5 pps  1 x: 1 to 8,191 pps  300 x: 300 to 2,457,300 pps                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Number of speed setting register                    | 3 registers : FL, FH1, and FH2                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Slow-down point (=ramping down point) setting range | 0 to 16,777,215 (24 bit)                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Characteristic of acceleration/deceleration         | Linear acceleration/deceleration     S-curve acceleration/deceleration                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Acceleration rate setting range                     | 1 to 65,535 (16 bit)                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Deceleration rate setting range                     | 1 to 65,535 (16 bit)                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Up/down counter                                     | -2,147,483,648 to +2,147,483,647 (32 bit)                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| General-purpose I/O terminal                        | 4 bits (2 bits are output fixed, 2 bits are input/output selectable)                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| The excitation sequence output                      | Excitation sequence output for stepping motors  Driving method: selection of unipolar drive or bipolar drive Excitation method: selection of full step or half step                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Typical operation example                           | Continuous movement by command control  Origin return movement by origin signal control  Origin return with feeding amount limit setting by origin signal control  Origin escape by origin signal control  EL escape by EL signal control  Incremental movement of positioning control  Timer by positioning control  Continuous movement and incremental movement by switch control  Continuous movement and incremental movement by manual pulser control |  |  |  |  |

| Ambient temperature                                 | -40 to + 85 °C                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Storage temperature                                 | −65 to + 150 °C                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Package                                             | 48 pin TQFP (7 x 7 mm: molded part)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Weight                                              | 0.13 g                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

### Note

- 1) During operation, the target position cannot be changed, in other words, target position override is not available. (Speed can be changed.)

- 2) During slow-down point auto setting, be sure to set the acceleration and deceleration characteristics to be the same.

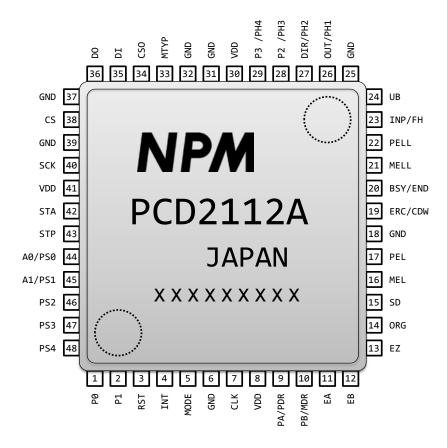

# 2.2 Terminal assignment diagram

Note: No. 1 pin is located at the bottom left with the type name making "1".

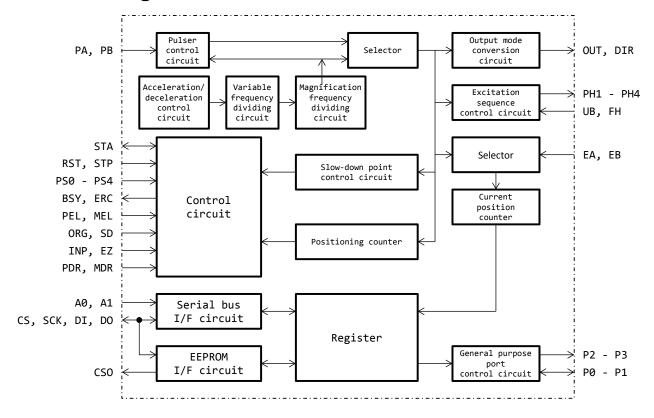

### 2.3 Block diagram

### 2.4 Terminal list

U/D column (internal circuit) PD: Pull-Down (40 k $\Omega$  to 240 k $\Omega$ ) built-in resistor, OD: Open drain. .....

Process column (when not in use) Open: unconnected,

(PD): connected to pull-down (5 k $\Omega$  to 10 k $\Omega$ ) or no connection. [PD]: Connected to pull-down (5 k $\Omega$  to 10 k $\Omega$ ), no connection or connected to GND.

[GN]: Connect to GND.

TTL column (TTL I/F) O: 5 V (TTL) I/F is OK. (Output terminals do not reach 5 V even if they are pulled up

externally).

| Pin      | Name       | I/O      | U/D     | Process   | TTL     | I <sub>OH</sub> | I <sub>OL</sub> | Description                                                          |  |

|----------|------------|----------|---------|-----------|---------|-----------------|-----------------|----------------------------------------------------------------------|--|

| 1        | P0         | 1/0      | PD      | (PD)      | 0       | -6 mA           | 6 mA            | General-purpose I/O terminal 0                                       |  |

|          | P1         | 1/0      | PD      | (PD)      | 0       | -6 mA           |                 | General-purpose I/O terminal 1                                       |  |

| 3        | RST        | 1/0      | PD      | (PD)      |         | -6 IIIA         | 6 mA            | ' '                                                                  |  |

| 4        |            | -        | OD      | -         | 0       | -<br>C A        | - C A           | Reset                                                                |  |

|          | INT        | 0        | _       | Open      | 0       | −6 mA           | 6 mA            | Interrupt request                                                    |  |

| 5        | MODE       |          | PD      | -         | 0       | -               | -               | Operation mode (L: CPU-connected, H: Stand-alone)                    |  |

| 6        | GND<br>CLK |          | -       | -         | -       | -               | -               | GND<br>Reference clock                                               |  |

| 7        | VDD        | _        | -       | -         | 0       | -               | -               | +3.3 V                                                               |  |

| <u>8</u> | PA/PDR     | - 1      | -<br>PD | [PD]      | 0       | -               | -               | Pulser A-phase / positive direction operation switch                 |  |

| _        | PB/MDR     | 1        | PD      | [PD]      | 0       | -               | -               | ·                                                                    |  |

| 11       | EA EA      | - !      | PD      | [PD]      | 0       |                 |                 | Pulser B-phase / negative direction operation switch Encoder A-phase |  |

|          |            | - 1      |         |           |         | -               | -               | '                                                                    |  |

| 12       | EB         | -        | PD      | [PD]      | 0       | -               | -               | Encoder B-phase                                                      |  |

| 13       | EZ         | !        | PD      | [PD]      | 0       | -               | -               | Encoder Z-phase                                                      |  |

| 14       | ORG        | <u>!</u> | PD      | [PD]      | 0       | -               | -               | Origin sensor                                                        |  |

| 15       | SD         | 1        | PD      | [PD]      | 0       | -               | -               | Deceleration sensor (common in ± moving direction)                   |  |

| 16       | MEL        | 1        | PD      | [PD]      | 0       | -               | -               | Negative direction end limit                                         |  |

| 17       | PEL        | - 1      | PD      | [PD]      | 0       | -               | -               | Positive direction end limit                                         |  |

| 18       | GND        | -        | -       | -         | -       |                 |                 | GND                                                                  |  |

|          | ERC/CDW    | 0        | -       | Open      | 0       | −12 mA          | 12 mA           | Deviation counter clear / current down                               |  |

|          | BSY/END    | 0        | -       | Open      | 0       | −12 mA          | 12 mA           | In operation (busy) / operation complete                             |  |

| 21       | MELL       | ı        | PD      | [GN]      | 0       | -               | -               | MEL signal input logic                                               |  |

| 22       | PELL       | I        | PD      | [GN]      | 0       | -               | -               | PEL signal input logic                                               |  |

| 23       | INP/FH     | - 1      | PD      | [PD]      | 0       | -               | -               | In-position / excitation mode: (L: Full step – H: Half step )        |  |

| 24       | UB         | - 1      | PD      | [PD]      | 0       | -               | -               | Drive mode: L: Unipolar, H: Bipolar                                  |  |

| 25       | GND        | - 1      | -       | -         | -       | -               | -               | GND                                                                  |  |

| 26       | OUT/PH1    | 0        | -       | Open      | 0       | −12 mA          | 12 mA           | Pulse train signal / 1-phase excitation signal                       |  |

| 27       | DIR/PH2    | 0        | -       | Open      | 0       | −12 mA          | 12 mA           | Operation direction signal/ 2-phase excitation signal                |  |

| 28       | P2/PH3     | 0        | PD      | Open      | 0       | −12 mA          | 12 mA           | General-purpose output terminal 2 / 3 phase excitation signal        |  |

| 29       | P3/PH4     | 0        | PD      | Open      | 0       | −12 mA          | 12 mA           | General-purpose output terminal 3 / 4 phase excitation signal        |  |

| 30       | VDD        | - 1      | -       | -         | -       | -               | -               | +3.3 V                                                               |  |

| 31       | GND        | - 1      | -       | -         | -       | -               | -               | Input terminal for shipping inspection (connect to GND)              |  |

| 32       | GND        | ı        | -       | ı         | -       | -               | -               | Input terminal for shipping inspection (connect to GND)              |  |

| 33       | MTYP       | - 1      | PD      | -         | 0       | _               | -               | Operation pulse selection                                            |  |

| - 0.4    | 000        | 0        |         | 0         |         | Ο Δ             | 0 1             | (L: Pulse train output, H: excitation sequence output)               |  |

| 34       | CSO        | 0        | -       | Open      | 0       | −6 mA           | 6 mA            | CS (Chip select) output for EEPROM                                   |  |

| 35       | DI         | I/O      | PD      | -         | $\circ$ | −6 mA           | 6 mA            | For serial communication: data input (output when MODE = H level)    |  |

|          |            |          |         |           | 0       |                 |                 | For serial communication: data output                                |  |

| 36       | DO         | I/O      | PD      | -         | 0       | −6 mA           | 6 mA            | (input when MODE = H level)                                          |  |

| 37       | GND        | I        | -       | -         | -       | -               | -               | GND                                                                  |  |

| 38       |            | I/O      | PD      | Open      | 0       | −6 mA           | 6 mA            | For serial communication: chip select input (outputs when MODE =     |  |

|          |            | 1/0      | Fυ      | Open      | 0       | -0 IIIA         | UIIIA           | H level)                                                             |  |

| 39       | GND        | 1        | -       | -         | -       | -               | -               | GND                                                                  |  |

| 40       | SCK        | I/O      | PD      | -         | 0       | -6 mA           | 6 mA            | For serial communication: synchronous clock input (outputs when      |  |

|          |            | ,        |         |           |         |                 |                 | MODE = H level)<br>+3.3 V                                            |  |

| 41       | STA        | I/O      | -<br>PD | -<br>Open | -       | -6 mA           | 6 mA            | External start                                                       |  |

|          | STP        | 1/0      | PD      | [PD]      |         | OIIIA           | UIIIA           | External stop                                                        |  |

|          |            | 1        |         |           | 0       | -               | _               | · ·                                                                  |  |

|          | A0/PS0     | 1        | PD      | [PD]      | 0       | -               | -               | LSI selection 0 / pattern selection 0                                |  |

|          | A1/PS1     | 1        | PD      | [PD]      | 0       | -               | -               | LSI selection 1 / pattern selection 1                                |  |

|          | PS2        | 1        | PD      | (PD)      | 0       | -               | -               | Pattern selection 2                                                  |  |

| 47       |            | 1        | PD      | (PD)      | 0       | -               | -               | Pattern selection 3                                                  |  |

| 48       | PS4        | I        | PD      | (PD)      | 0       | -               | -               | Pattern selection 4                                                  |  |

### 2.5 System modes

have been written in the EEPROM.

With PCD2112A, the following four types of systems can be selected by MODE terminal and MTYP terminal. Do not change the settings while the power is ON. Some input terminals may change to output terminals if the settings are changed. Be careful when designing an external circuit.

- CPU-connected pulse train output system (MODE = L, MTYP = L)

4-wire serial bus is connected to CPU for control. Pulse train signals are output.

- CPU-connected excitation sequence output system (MODE = L, MTYP = H)

4-wire serial bus is connected to CPU for control. Excitation sequence signals are output.

Excitation sequence can be selected from four types depending on UB terminal and FH terminal.

- Stand-alone pulse train output system (MODE = H, MTYP = L)

Reads the operation patterns specified by PS0 to PS4 terminals from an external EEPROM; up to 32 operation patterns

Pulse train signals are output according to the operation pattern.

CPU is required to write patterns to EEPROM, but it is not required for operation.

4) Stand-alone excitation sequence output system (MODE = H, MTYP = H)

Reads the operation patterns specified by PS0 to PS4 terminals from an external EEPROM; up to 32 operation patterns

have been written in the EEPROM. Excitation sequence signals are output according to the operation pattern.

CPU is required to write patterns to EEPROM, but is not required for operation.

The excitation sequence can be selected from four types depending on UB terminal and FH terminal.

|                       | System mo           | MODE     | MTYP      | UB | FH    |   |       |

|-----------------------|---------------------|----------|-----------|----|-------|---|-------|

|                       | Pulse train output  |          |           | L  | L     | L | (INP) |

| CPU-connected         |                     | Unipolar | Full-step |    | Н     | L | L     |

| operation             | Excitation sequence | Unipolal | Half-step | L  | Η     | ١ | Н     |

| operation             | output              | Bipolar  | Full-step | L  | Η     | Ι | L     |

|                       |                     |          | Half-step | L  | Η     | Ι | Н     |

|                       | Pulse train output  | Н        | L         | L  | (INP) |   |       |

| Ctand along           |                     | Unipolar | Full-step | Н  | Н     | L | L     |

| Stand-alone operation | Excitation sequence | Unipolal | Half-step | Н  | Η     | ١ | Н     |

|                       | output              | Pipelor  | Full-step | Н  | Н     | Ι | Ĺ     |

|                       |                     | Bipolar  | Half-step | Н  | Н     | Ι | Н     |

Note 1: In pulse train output mode, UB terminal is disabled.

UB terminal has a built-in pull-down resistor, so set to L-level to lower the current consumption.

Note 2: In pulse train output mode, INP/FH terminal become INP terminal.

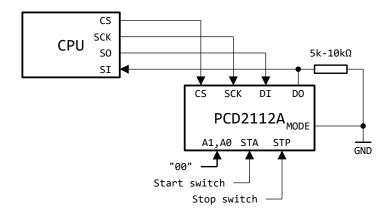

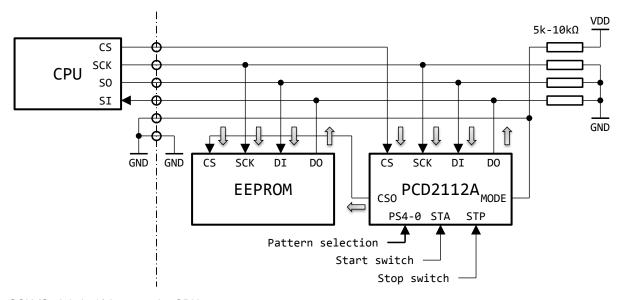

### 2.5.1 CPU-connected system (MODE = L)

PCD2112A is connected to CPU by 4-wire serial I/F.

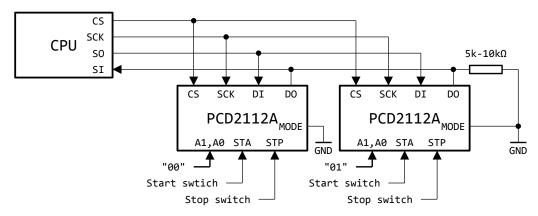

Multiple LSIs can be connected with one CS output.

To control products other than "PCD2112A", prepare CS output separately.

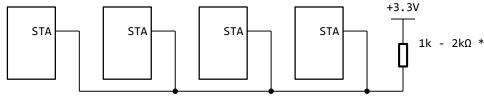

### 1) Normal connection

Both start and stop can be done from CPU.

Note: Connect a pull-down resistor for the purpose of preventing breakage of CPU and PCD2112A when floating.

### 2) Multiple connections

Both start and stop can be done from CPU.

Note: Connect a pull-down resistor to prevent CPU and PCD2112A from a breakage when floating.

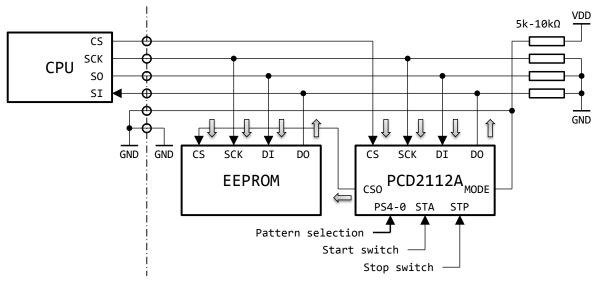

### 2.5.2 Stand-alone operation system (MODE = H)

An operation is selected by pattern selection terminals to perform. Up to 32 types of operation patterns have been stored in the 4-wire serial EEPROM. In the stand-alone operation system, this LSI and EEPROM are used in one configuration for one serial I/F. Writing to EEPROM is done by CPU-connected system.

In this case, CSO terminal of "PCD2112A" is connected to CS terminal of EEPROM, so do not connect CS terminal of CPU to CS terminal of EEPROM.

Note: External pull-down of SCK, DI, and DO terminals in the circuit diagram below can be done by pull-up. Pull-down can reduce the power consumption of the board.

### 1) Writing to EEPROM

Writing operation patterns to EEPROM is performed from CPU with separately prepared CPU.

SCK (Serial clock) is output by CPU.

CS (Chip select) for PCD2112A is also output by CPU and CS for EEPROM is output via CSO of PCD2112A. SO/SI (Serial data) is used in common between CPU and EEPROM, and also between CPU and PCD2112A.

Note: PS0 and PS1 terminals for pattern selection are A0 and A1 terminals for LSI selection respectively because they are used in CPU-connected system.

When communicating with CPU, match the set values of A0 and A1 terminals and bits 4 and 5 in bus control command.

### 2) When performing an stand-alone operation system

After writing operation patterns and stored them in an EEPROM, CPU can be disconnected before an operation. In the circuit shown below, MODE signal becomes H level when CPU is disconnected.

SCK (Serial clock) and CS (Chip Select) are output by PCD2112A. SO/SI (Serial data) is communicated between PCD2112A and EEPROM.

# 3. Terminal descriptions

# 3.1 Outline of terminal functions

|          | Terminal name            | Terminal number              | I/O | Logic setting | Description                                             |  |  |  |  |  |

|----------|--------------------------|------------------------------|-----|---------------|---------------------------------------------------------|--|--|--|--|--|

| Pov      | Power supply input       |                              |     |               |                                                         |  |  |  |  |  |

|          | VDD                      | 8, 30, 41                    | ı   | -             | +3.3 V                                                  |  |  |  |  |  |

|          | GND                      | 6, 18, 25, 31, 32,<br>37, 39 | I   | -             | GND                                                     |  |  |  |  |  |

| Sys      | System selection         |                              |     |               |                                                         |  |  |  |  |  |

|          | MODE                     | 5                            | I   | -             | L: CPU-connected system H: Stand-alone operation system |  |  |  |  |  |

|          | MTYP                     | 33                           | ı   | -             | L: Pulse train H: Excitation sequence                   |  |  |  |  |  |

| Ser      | al communication (MODE = |                              |     | l .           | _                                                       |  |  |  |  |  |

|          | cs                       | 38                           | I   | -             | For serial communication: chip select input             |  |  |  |  |  |

|          | SCK                      | 40                           | I   | -             | For serial communication:<br>Synchronous clock input    |  |  |  |  |  |

|          | DI                       | 35                           | ı   | -             | For serial communication: data input                    |  |  |  |  |  |

|          | DO                       | 36                           | 0   | _             | For serial communication: data output                   |  |  |  |  |  |

| Ser      | al communication (MODE = |                              | )   | I             | 11 of Contai Communication, data Output                 |  |  |  |  |  |

|          | CS CS                    | 38                           | 0   | -             | Not used                                                |  |  |  |  |  |

|          | SCK                      | 40                           | 0   | -             | For serial communication: synchronous clock output      |  |  |  |  |  |

|          | DI                       | 35                           | 0   | _             | For serial communication: data output                   |  |  |  |  |  |

|          | DO                       | 36                           |     | _             | For serial communication: data output                   |  |  |  |  |  |

| For      | motion control           | 00                           |     |               | i or serial communication, data input                   |  |  |  |  |  |

| l        | RST                      | 3                            | ı   | _             | Reset                                                   |  |  |  |  |  |

|          | CLK                      | 7                            | i   | -             | Reference clock                                         |  |  |  |  |  |

|          | A0, A1                   | 44, 45                       | i   | -             | LSI selection                                           |  |  |  |  |  |

|          | INT                      | 4                            | 0   | -             | Interrupt request                                       |  |  |  |  |  |

|          | BSY/END                  | 20                           | 0   | -             | Busy / Operation end                                    |  |  |  |  |  |

|          | ERC/CDW                  | 19                           | 0   | RENV1.ERCL    | Deviation counter clear / Current down                  |  |  |  |  |  |

|          | INP                      | 23                           | I   | RENV1.INPL    | In-position (positioning completes)                     |  |  |  |  |  |

|          | STA                      | 42                           | I/O | -             | External start                                          |  |  |  |  |  |

|          | STP                      | 43                           | ı   | RENV1.STPL    | External stop                                           |  |  |  |  |  |

|          | P0, P1                   | 1, 2                         | I/O | -             | General-purpose I/O terminals 0 and 1                   |  |  |  |  |  |

|          | P2, P3                   | 28, 29                       | 0   | -             | General purpose output terminals 2 and 3                |  |  |  |  |  |

| For      | sensor input             |                              |     |               |                                                         |  |  |  |  |  |

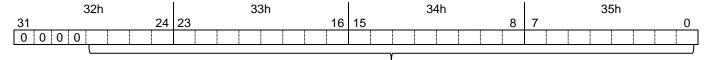

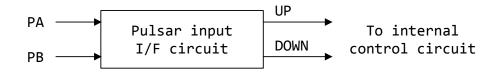

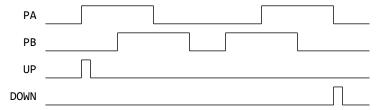

|          | PA, PB                   | 9, 10                        | I   | RENV2.PIM     | Manual pulser                                           |  |  |  |  |  |

|          | PDR, MDR                 | 9, 10                        | I   | RENV1.DRL     | Drive switch                                            |  |  |  |  |  |

|          | EA, EB                   | 11, 12                       | ı   | RENV2.EIM     | Encoder                                                 |  |  |  |  |  |

|          | EZ                       | 13                           |     | RENV2.EZL     | Encoder Z phase                                         |  |  |  |  |  |

|          | PELL, MELL               | 22, 21                       |     | -             | EL signal input logic                                   |  |  |  |  |  |

|          | PEL, MEL                 | 17, 16                       |     | PELL, MELL    | End limit sensor                                        |  |  |  |  |  |

|          | ORG                      | 14                           |     | RENV1.ORGL    | Origin sensor                                           |  |  |  |  |  |

|          | SD                       | 15                           | I   | RENV1.SDL     | Deceleration sensor                                     |  |  |  |  |  |

| For      | motor drive              |                              |     |               |                                                         |  |  |  |  |  |

|          | OUT, DIR                 | 26, 27                       | 0   | RENV1.PMD     | Output pulse                                            |  |  |  |  |  |

|          | FH                       | 23                           | I   | -             | L: Full step, H: Half step                              |  |  |  |  |  |

|          | UB                       | 24                           | I   | -             | L: Unipolar drive, H: Bipolar drive                     |  |  |  |  |  |

|          | PH1, PH2, PH3, PH4       | 26, 27, 28, 29               | 0   | -             | Excitation sequence                                     |  |  |  |  |  |

| For      | stand-alone operation    |                              |     |               |                                                         |  |  |  |  |  |

|          | CSO                      | 34                           | 0   | -             | Chip select for EEPROM                                  |  |  |  |  |  |

| <u> </u> | PS0, PS1, PS2, PS3, PS4  | 44, 45, 46, 47, 48           | ı   | -             | Pattern selection; 0 to 4                               |  |  |  |  |  |

Note: The above table classifies the functions, and some terminals have multiple functions (share the same terminal numbers).

# 3.2 Terminal functions in each system mode

Functions of the following terminals will be changed depending on the system mode.

|         | ode     |                   |                                                               | nnected syste     | em                         |                   |        | e operation system         |     |

|---------|---------|-------------------|---------------------------------------------------------------|-------------------|----------------------------|-------------------|--------|----------------------------|-----|

|         | \       | Pulse trai        | Pulse train output Excitation sequence output Pulse train out |                   | Excitation sequence output |                   | output | Excitation sequence output |     |

| Termina | al name | Terminal function | I/O                                                           | Terminal function | I/O                        | Terminal function | I/O    | Terminal function          | I/O |

| 5       | MODE    | (Low)             |                                                               | (Low)             | I                          | (High)            | I      | (High)                     | I   |

| 33      | MTYP    | (Low)             |                                                               | (High)            | I                          | (Low)             | I      | (High)                     | I   |

| 40      | SCK     | SCK               |                                                               | SCK               | I                          | SCK               | 0      | SCK                        | 0   |

| 35      | DI      | DI                |                                                               | DI                | I                          | DI                | 0      | DI                         | 0   |

| 36      | DO      | DO                | 0                                                             | DO                | 0                          | DO                | I      | DO                         |     |

| 38      | cs      | cs                | I                                                             | cs                | Ι                          | (Same as<br>CSO)  | 0      | (Same as CSO)              | 0   |

| 44      | A0/PS0  | A0                | I                                                             | A0                | I                          | PS0               | I      | PS0                        | I   |

| 45      | A1/PS1  | A1                | I                                                             | A1                | I                          | PS1               | I      | PS1                        | I   |

| 46      | PS2     | (*)               |                                                               | (*)               | 1                          | PS2               | ı      | PS2                        | I   |

| 47      | PS3     | (*)               |                                                               | (*)               | 1                          | PS3               | I      | PS3                        | I   |

| 48      | PS4     | (*)               |                                                               | (*)               | 1                          | PS4               | ı      | PS4                        | I   |

| 1       | P0      | P0                | I/O                                                           | P0                | I/O                        | (*)               | 0      | (*)                        | 0   |

| 2       | P1      | P1                | I/O                                                           | P1                | I/O                        | (*)               | 0      | (*)                        | 0   |

| 24      | UB      | (*)               |                                                               | UB                | I                          | (*)               | I      | UB                         | I   |

| 23      | INP/FH  | INP               |                                                               | FH                | I                          | INP               | I      | FH                         | I   |

| 26      | OUT/PH1 | OUT               | 0                                                             | PH1               | 0                          | OUT               | 0      | PH1                        | 0   |

| 27      | DIR/PH2 | DIR               | 0                                                             | PH2               | 0                          | DIR               | 0      | PH2                        | 0   |

| 28      | P2/PH3  | P2                | 0                                                             | PH3               | 0                          | (*)               | 0      | PH3                        | 0   |

| 29      | P3/PH4  | P3                | 0                                                             | PH4               | 0                          | (*)               | 0      | PH4                        | 0   |

Note 1: For terminals with multiple names (=multiple functions), the name / function will be selected by "Environment setting register".

Note 2: "(Low)" and "(High)" indicate the level to be set for input.

<sup>(\*):</sup> Please pull down (with 5 kΩ to 10 kΩ).

### 3.3 Terminal functions

### 3.3.1 CLK [7]

Input terminal of reference clock. (Standard: 9.8304 MHz)

The accuracy of reference clock frequency affects the speed accuracy of output pulses.

It also affects start timing, input sensitivity of STA, ORG, MEL, PEL, and STP signals, and write/read timing.

### 3.3.2 RST [3]

Input terminal of reset signals.

Inputs 8 or more CLK signals while "RST = L".

Then, you can use it after inputting 8 or more CLK signals while "RST = H".

Be sure to reset at least once after turning ON the power and before starting an operation.

The status after the reset is shown in the table below:

| Item                                          | Reset status (Default status) |

|-----------------------------------------------|-------------------------------|

| Internal register                             | 0                             |

| Control command                               | 0                             |

| P0 ~ P1 terminal                              | Input terminal (*1)           |

| OUT and DIR terminals                         | H level                       |

| INT terminal                                  | H level                       |

| ERC/CDW terminal                              | H level                       |

| BSY/END terminal                              | H level                       |

| PH1, PH2, PH3 and PH4 terminal                | STEP0 sequencing status (*2)  |

| P2 and P3 terminals (MTYP terminal = L level) | L level                       |

<sup>\*1:</sup> It may be an output terminal between power ON and resetting.

### 3.3.3 MODE [5]

Input terminal for setting "System mode" of PCD2112A. For information on "System mode", see "2.5 System modes".

| MODE | System mode                                     |  |  |  |  |  |

|------|-------------------------------------------------|--|--|--|--|--|

| L    | CPU-connected system                            |  |  |  |  |  |

| Н    | Stand-alone operation system (EEPROM connected) |  |  |  |  |  |

### 3.3.4 MTYP [33]

Input terminal for selecting the motor control method.

| MTYP | Mode                            | Description                                                                                                                                                                                                                                                   |  |  |  |  |  |

|------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| L    | Pulse train output mode         | INP/FH terminal functions as INP inputs. DIR/PH1 terminal outputs pulse trains. DIR/PH2 terminal outputs direction signals. P2/PH3 terminal functions as general-purpose output terminal P2. P3/PH4 terminal functions as general-purpose output terminal P3. |  |  |  |  |  |

| н    | Excitation-sequence output mode | INP/FH terminal functions as FH input. OUT/PH1 to P3/PH4 terminals output excitation sequence signals.                                                                                                                                                        |  |  |  |  |  |

<sup>\*2 :</sup> See "10.6.2 PH1 to PH4 signals".

### 3.3.5 INT [4]

Output terminal for interrupt request (INT) signals to CPU.

Multiple LSIs can be wired-OR connected by using a pull-up resistor (5 k $\Omega$  to 10 k $\Omega$ ) to the outside.

When an interrupt condition occurs, it becomes "L level".

The interrupt conditions are set by bits 22 to 17 of RENV2 register.

You can mask the outputs with RENV2.MSKI bit.

INT signal can be output by stopping with EL, STP, or SD signal without setting the interrupt condition.

### 3.3.6 SCK [40], DI [35], DO [36], CS [38], CSO [34]

The following are the terminals for serial communication:

| Setting Terminal name | MODE = L (CPU-connected system)                                                                             | MODE = H (Stand-alone operation system)   |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

| SCK                   | Synchronous clock input of serial signal                                                                    | Synchronous clock output of serial signal |  |

| DI                    | Serial input signal                                                                                         | Serial output signal                      |  |

| DO                    | Serial output signal                                                                                        | Serial input signal                       |  |

| CS                    | Chip select Input                                                                                           | The same signal as CSO is output.         |  |

| CSO                   | Chip select output to EEPROM (when both PCD2112A and EEPROM are controlled by CPU $_{\star}$ using one CS). |                                           |  |

<sup>\*:</sup> They can be opened when they are not in use.

### 3.3.7 PA/PDR [9], PB/MDR [10]

Used when "RMD.MOD = 7h to Ah".

It works as follows in accordance with RMD.MOD bit.

| Setting Terminal name | RMD.MOD = 9h, Ah   | RMD.MOD = 7h, 8h   |  |

|-----------------------|--------------------|--------------------|--|

| PA/PDR                | PA (manual pulser) | PDR (drive switch) |  |

| PB/MDR                | PB (manual pulser) | MDR (drive switch) |  |

PA, PB: Input signals from a manual pulser.

A motor can be operated in synchronization with a manual pulser.

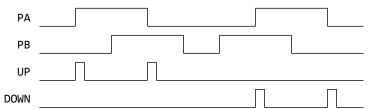

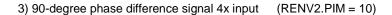

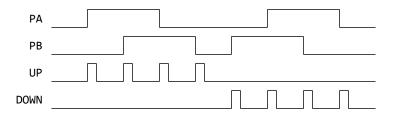

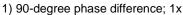

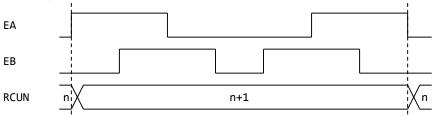

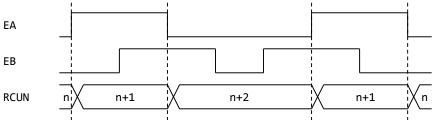

PA/PB signal input specifications can be selected by the software: 2-pulses or 90-degree phase difference

(1x, 2x or 4x) by using RENV2.PIM bit.

PDR, MDR: Input the signal from a drive switch.

A motor can be operated only while the drive switch is ON, or it can be operated only by a certain amount

every time the drive switch is ON.

The input logic can be selected using RENV1.DRL bit.

Noise filters can be inserted into PA/PDR and PB/MDR terminals using RENV2.PINF bit.

The states of PA and PB terminals can be monitored by RSTS.SPA bit and RSTS.SPB bit.

### 3.3.8 A0/PS0 [44], A1/PS1 [45], PS2 [46], PS3 [47], PS4 [48]

In stand-alone operation system (MODE = H), the terminals become PS0 to PS4 for selecting an operation pattern. In CPU-connected system (MODE = L), the terminals become A0 and A1 for LSI selection.

In either case, the input logic is positive. (0: L level, 1: H level)

| Setting Terminal name | MODE = L-level<br>(CPU-connected system) | MODE = H-level<br>(Stand-alone operation system) |

|-----------------------|------------------------------------------|--------------------------------------------------|

| A0/PS0                | A0: LSI selection 0                      | PS0: Operation pattern setting 0                 |

| A1/PS1                | A1: LSI selection 1                      | PS1: Operation pattern setting 1                 |

| PS2                   | (*)                                      | PS2: Operation pattern setting 2                 |

| PS3                   | (*)                                      | PS3: Operation pattern setting 3                 |

| PS4                   | (*)                                      | PS4: Operation pattern setting 4                 |

Select the LSI whose setting value of LSI selection is the same as bits 5 and 4 of the bus control command to perform serial communication. Therefore, up to four LSIs can be connected to one set of serial buses.

### (\*): Be sure to pull down (5 k $\Omega$ to 10 k $\Omega$ ).

When input level changes during operation, an emergency stop occurs and RCUN register (current position counter) is reset.

Even in a stand-alone operation, an emergency stop occurs when the input levels of PS0 to PS4 terminals change during an operation.

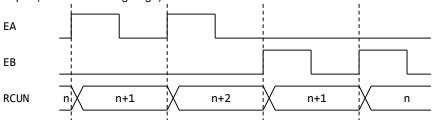

### 3.3.9 EA [11], EB [12], EZ [13]

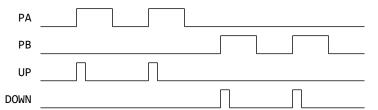

EA and EB terminals are for encoder signal input:

The input specification is specified by RENV2. EIM bit. The input specification can be selected from either 2-pulse input or 90-degree phase differences (1x, 2x or 4x) input.

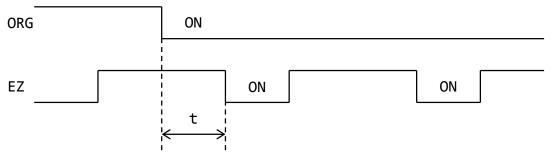

EZ terminal is an input terminal for encoder Z-phase signal, and it can be used in the operation mode for origin return. Each terminal can be monitored by RSTS.SEA bit, RSTS.SEB bit or RSTS.SEZ bit.

### 3.3.10 BSY/END [20]

Output a signal indicating that an operation is in progress or is completed. It functions as shown below depending on RENV1.ENDM bits.

| Setting<br>Terminal name | RENV1.ENDM = 0            | RENV1.ENDM = 1               |  |

|--------------------------|---------------------------|------------------------------|--|

| BSYEND                   | BSY<br>(During operation) | END<br>(Operation completed) |  |

BSY: Outputs L level during operation and returns to H level upon end of the operation.

END: Outputs L level when an operation is ended with "STA = L level", and returns to H level by setting STA = H level.

For the difference between BSY and END signals, see "10.2 Operation status check output"

### 3.3.11 SD [15]

Input terminal for deceleration signals:

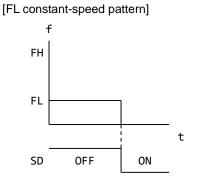

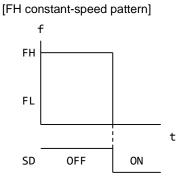

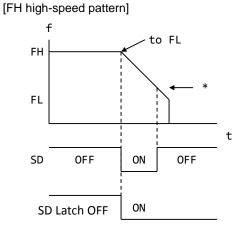

RMD.MSDE bit allows you to select either this signal is enabled or disabled. Input logic can be selected by RENV1.SDL bit. RENV1.SDM bit allows you to select either "decelerate" or "decelerate and stop" when this signal is ON.

When "decelerate" is selected, deceleration starts when SD signal is turned ON, and it accelerates again when SD signal turns OFF again.

When deceleration stop is selected, it accelerates again if it returns to OFF during deceleration. If deceleration stop is selected, it remains stopped even if it returns to OFF after stopping.

If the latch function is enabled by "RENV1.SDLT = 1", deceleration stop can be performed even if spike-shaped signals are input. The input state is latched at start, and thereafter the change from input OFF to ON will be stored.

SD terminal status can be monitored by RSTS.SSD bit.

Latching state of SD signal can be monitored by RSTS.SDIN bit.

### 3.3.12 PELL [22], MELL [21]

Terminals to set the input logic of EL signal through hardware.

Select the logic of PEL signal by PELL terminal, and select the logic of MEL signal by MELL terminal.

| ELL terminal | Operation                                        |

|--------------|--------------------------------------------------|

| L            | Input of EL signal operates with positive logic. |

| Н            | Input of EL signal operates with negative logic. |

### 3.3.13 PEL [17], MEL [16]

Input terminals for EL signals. Input logic can be specified by PELL, MELL terminals.

When EL signal in the moving direction turns ON, the operation stops immediately. Even if returning to OFF, the operation remains stopped.

When EL signal in the moving direction is ON at start, the stop state is maintained.

When timer is selected as the operation mode, EL signal is disabled.

EL terminal state can be monitored by RSTS.SPEL bit and RSTS.SMEL bit.

### 3.3.14 ORG [14]

As for input terminal for origin signal, input logic can be specified by RENV1.ORGL bit.

When the operation mode is origin return (RMD.MOD = 1h, 2h), the operation stops immediately when ORG signal changes from OFF to ON. After that, the operation remains stopped even if this signal returns to OFF.

Please note that operation will never stop if you start with ORG signal ON.

When the operation mode is origin escape (RMD.MOD = 3h), the operation stops immediately when ORG signal turns OFF. After that, the operation remains stopped even if the signal returns to ON.

Also, if you start with ORG signal OFF, the stop state is maintained.

ORG terminal state can be monitored by RSTS.SORG bit.

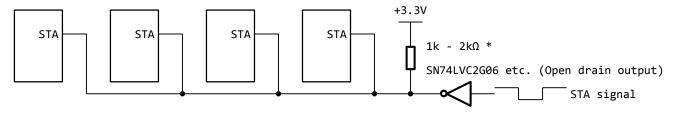

### 3.3.15 STA [42]

I/O terminal for external starts

An external start requires an external pull-up resistor.

When "RMD.MSY = 1" is set, an operation starts at the falling edge of STA signal after a start command is input.

Be sure to drive the external circuit with an open drain.

Signals less than 5 cycles of the reference clock are not accepted.

Writing STAO commands enables to output one-shot pulse.

STA terminal state can be monitored by RSTS.SSTA bit.

See "10.7 External start and simultaneous start" for details.

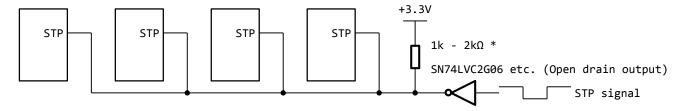

### 3.3.16 STP [43]

Input terminal for an external stop.

Input logic can be selected with RENV1.STPL bit.

Use RMD.MSPE bit to specify whether STP signal is abled or disabled.

RENV1.STPM bit is used to select either "immediate stop" or "deceleration stop" by STP signal.

Even if this signal returns to OFF after stopping, it remains stopped.

If STP signal is ON at start, the operation does not start.

STP terminal state can be monitored by RSTS.SSTP bit.

See "10.8 External stop" for details.

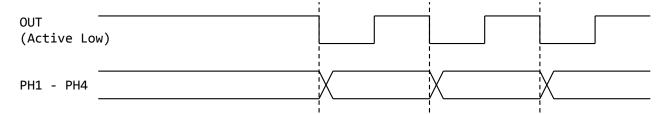

### 3.3.17 OUT/PH1 [26], DIR/PH2 [27]

With MTYP terminal, they function as follows:

| Setting Terminal name | MTYP = L<br>(Pulse train output mode) | MTYP = H (Excitation sequence output mode) |  |

|-----------------------|---------------------------------------|--------------------------------------------|--|

| OUT/PH1               | OUT output                            | PH1 output                                 |  |

| DIR/PH2               | DIR output                            | PH2 output                                 |  |

OUT, DIR: Pulse output terminal for driving a motor.

RENV1.PMD bit allows you to specify from eight types of output specification.

Mask the pulse output when the operation mode is "positioning control - timer". Direction signal is output.

PH1, PH2: Phase signal for stepping motors is output.

Phase distribution signal for stepping motors is output together from P2/PH3 and P3/PH4 terminals.

Output mode changes depending on UB and FH terminals. PH1 to PH4 terminal status can be monitored by RSTS.SPH bit.

Excitation sequence is not switched when Operation mode is "positioning control - timer".

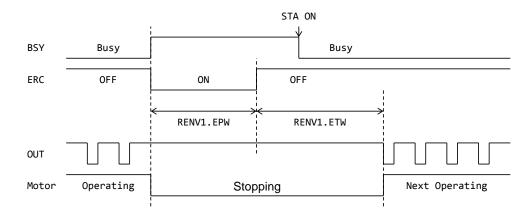

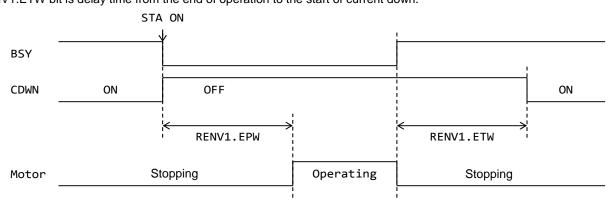

### 3.3.18 ERC/CDW [19]

The following signals can be specified by RENV1.CDWS bit.

| Setting<br>Terminal name | CDWS = 0   | CDWS = 1   |

|--------------------------|------------|------------|

| ERC/CDW                  | ERC output | CDW output |

ERC: Deviation counter clear signal is output for servo motor system.

CDW: Current down signal is output for stepping motors.

ERC/CDW signal logic can be changed by RENV1.ERCL bit. ERC/CDW terminal state can be monitored by RSTS.SERC bit.

### 3.3.19 UB [24]

Input terminal to set the drive mode.

UB terminal state can be monitored by RSTS.SPUB bit.

| UB terminal | Operation                                                                |

|-------------|--------------------------------------------------------------------------|

| L           | Outputs excitation sequence of unipolar drive from PH1 to PH4 terminals. |

| Н           | Outputs excitation sequence of bipolar drive from PH1 to PH4 terminals.  |

When pulse train output mode (MTYP = L) is selected, connect with pull-down (5 k $\Omega$  to 10 k $\Omega$ ), unconnected or connect directly to GND.

### 3.3.20 INP/FH [23]

Depending on MTYP input terminal state, the terminal function is as follows:

| Setting<br>Terminal name | MTYP = L<br>(Pulse train output mode) | MTYP = H (Excitation sequence output mode) |

|--------------------------|---------------------------------------|--------------------------------------------|

| FH/INP                   | INP input                             | FH input                                   |

NP: Input terminal for in-position signal (=positioning complete signal).

Input signal from a servo motor driver.

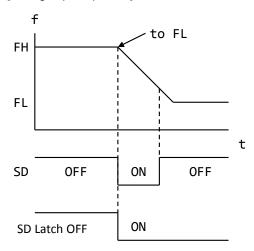

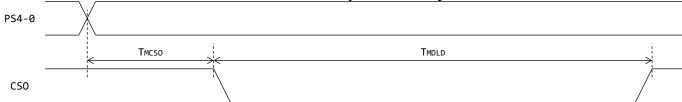

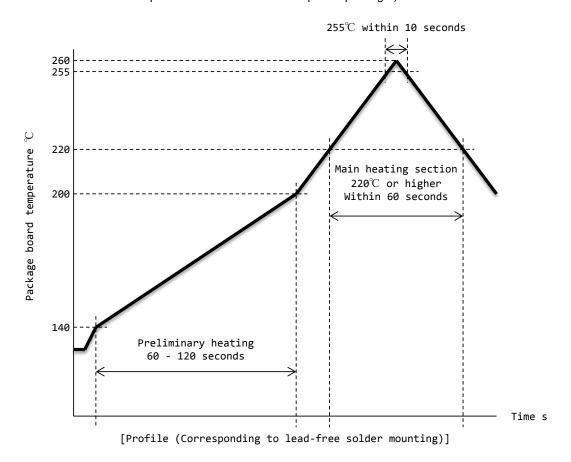

You can set operation complete when the motor stops after pulse output is completed.